### SSLC, HSE, DIPLOMA, B.E/B.TECH, M.E/M.TECH, MBA, MCA

Notes

Syllabus

Question Papers

Results and Many more

Available @ www.AllAbtEngg.com

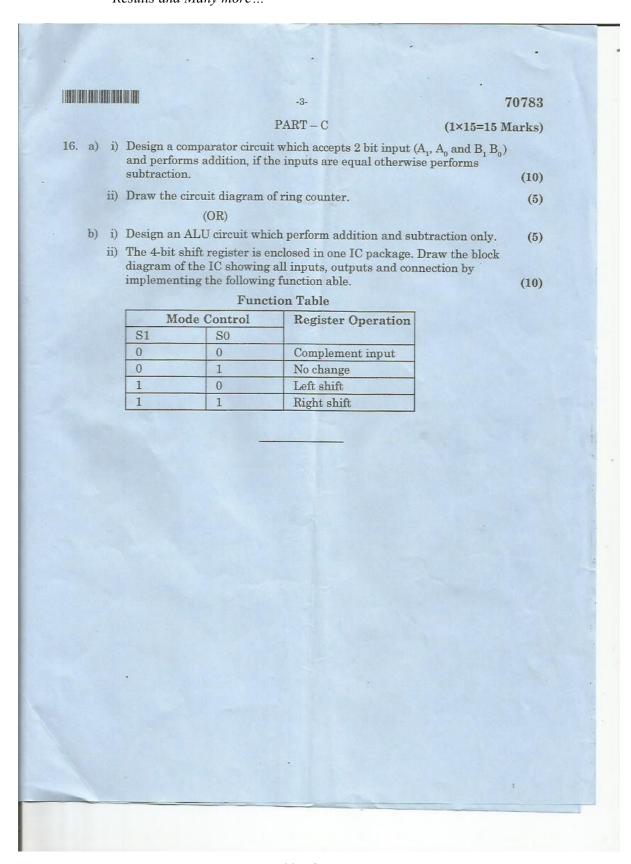

Results and Many more... Reg. No.: Question Paper Code: 70783 M.C.A. DEGREE EXAMINATIONS, NOVEMBER/DECEMBER 2019 First Semester MC5101 - COMPUTER ORGANIZATION (Regulations 2017) Time: Three Hours Maximum: 100 Marks Answer ALL questions PART - A (10×2=20 Marks) 1. State absorption law. Find the binary equivalent of the given hexadecimal number A052. 3. Name a gate which can simulate a comparator. What are the comparisons performed by it? 4. List two applications of decoders. 5. What is a normalized floating point number? How is it stored in IEEE standard? 6. What is program counter? How does it sequence instruction execution? 7. What is operand forwarding? 8. Give two examples for control hazard. 9. Draw a block schematic of I/O connected as a daisy chain. 10. Define cache miss.

## www.AllAbtEngg.com

Available in / AllAbtEngg Android App too,

## SSLC, HSE, DIPLOMA, B.E/B.TECH, M.E/M.TECH, MBA, MCA

Notes Syllabus Question Papers Results and Many more...

Available @ www.AllAbtEngg.com

70783 (5×13=65 Marks) PART - B 11. a) i) Draw the logic circuit using two input NAND gate to implement the following function :  $F(A, B, C, D) = (A \oplus B)' + AB$ . (3) ii) Find the simplest sum of products form of the function using Quine (10)McClusky method f = wxyz' + wxy'z + w'xyz' + wx'yz' + wxyz.b) i) Draw a multiple level NOR circuit for the following expression: (3) AB'E + CD'E + BC.ii) Simplify the following two function using K-map: •  $F = \overline{A}\overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C}\overline{D} + ABC\overline{D} + \overline{A}BCD + \overline{A}\overline{B}C\overline{D} + \overline{A}BC\overline{D} + A\overline{B}C\overline{D}$ (10)•  $F(w, x, y, z) = \pi M(2, 3, 5, 5, 7, 8, 12, 14).$ 12. a) i) Design and implement a mod-4 counter that occurs in the following repeated sequence 000-->010-->011-->100-->000 using JK FF. (10) Mention the State diagram, State table and State equation. (3) (3) i) State the significance of a high priority encoder. (10) Design a full subtractor using 2 × 4 decoder and appropriate gates. 13. a) i) Explain the instruction set architecture and also discuss the different (10)addressing modes. ii) Describe the floating point representation that uses excess 127 format. (3) b) Draw the block schematic for floating point operation and explain arithmetic (13)operation for floating point numbers. 14. a) Explain the different hazards in pipe lined processor with examples. (13)b) Consider a single data path processor and explain the sequence of control (13)signal involved in executing ADD R1, R2 instruction. 15. a) Discuss the cache block replacement policy of FIFO, LRU and MRU for a cache implemented with direct mapping scheme. Compare the policy in terms of miss rate. b) Draw and explain the block diagram of DMA controller and also discuss the (13)different bus arbitration approaches in DMA.

# www.AllAbtEngg.com

### SSLC, HSE, DIPLOMA, B.E/B.TECH, M.E/M.TECH, MBA, MCA

Notes Syllabus Question Papers Results and Many more...

www.AllAbtEngg.com

Available @

www.AllAbtEngg.com

Available in / AllAbtEngg Android App too,